Clocked busses often need impedance controlled tracking to avoid the posibility of false clock signals caused by an impedance mismatch. As semiconductor devices have become faster and faster they have become much more susceptible to issues caused by signal noise. The problem relates to any type of clocked interface where a device you will transfer data to or from automatically moves on to the next data bit, byte or word every time it see’s a new clock edge.

The Cause

Until relatively recent times digital PCB design (and especially when prototyping) could be viewed as simply a means to electrically interconnect components and unless you designed RF circuits there was little else to worry about. However the PCB itself, or the means of connecting the components used (i.e. prototyping), is now is a very common cause of a loss of signal integrity. The reason is mainly due to the rise and fall times of output signals having decreased as devices are designed to operate faster and faster and to use smaller and smaller silicon manufacturing processes. This problem is not actually due to the operating frequency of a device or the frequency at which a signal is changing, it is due to the speed at which a signal output changes state from high to low and low to high. A signal doesn’t instantaneously change from high to low or low to high, it takes a certain amount of time which will be specified as the rise and fall time in a devices data sheet. Previous signal rise and fall times of many 10’s of nano seconds have now become times measured in just a few nano seconds or for many devices they are measured in pico seconds.

So you may be thinking, this can’t possibly be an issue for me, my board is only operating at a few MHz and I’ve even slowed my data bus down to a few KHz. Well unfortunately that doesn’t matter. If you work with a DC signal the only thing you really care about in a wire or PCB track is its resistance, which for short lengths will be close to zero. However, when using that wire or PCB track with a fast AC signal it starts to behave like a capacitor and inductor. Capacitors and inductors exhibit resistance to alternating current called reactance. The impedance of the wire or track is the vector sum of resistance and reactance, essentially the total resistance seen at a particular frequency. What happens when you send a signal with a fast rising and falling edge down a wire or PCB track, if the impedance of the gate driving the wire or track isn’t exactly the same as the one receiving the it, is it that some of the pulse bounces (literally) back to the driving gate. As there is still an impedance mismatch, the signal continues to bounce between the two until it finally dampens out. This bouncing becomes worse as the speed of signal rise and fall times increases. Basically, the faster rise and fall times of signals from modern semiconductors combined with wire or PCB trace inductance and capacitance causes noise signals of a greater magnitude than before. Greater magnitude means the bouncing signals can reach the threshold voltage required for the receiving device to ‘see’ another clock pulse, or an incorrect data level at the moment it is sampling the data line. The solution is to design your PCB to use impedance controlled tracks on these clocked connections.

Single Connections

Download the free Saturn PCB Design Toolkit – its a great tool for this. Use it as follows:

Select Conductor Impedance

Select Imperial or Metric (you can select later and it will auto convert all values)

Set copper weights and plating thickness (e.g. 18um copper + 18um plating = 35micros (1oz))

Select internal or external layers (typically microstrip or embedded microstrip)

Enter substrate options (prepreg dielectric constant – typical PCB’s are FR4)

Enter track width in conductor width

Enter prepreg height in conductor height (the distance between the copper layers excluding their thickness)

Click ‘solve’

Now adjust the track width until you get the impedance (Zo) you need. This is the thickness to make your tracks

100ohm Single Track Impedance (General signals, SPI bus etc)

General signals, SPI bus, etc will generally perform well with a 100ohm track Impedance. Some examples track widths with a GND plane under the tracks:

2 layer 1.6mm PCB (1.48mm FR4) = 0.61mm (100.3150ohms)

4 layer Multi-cb – Internal to Internal (1.2mm FR4) = 0.32mm (100.2269ohms)

4 layer Multi-cb – Internal to External (0.14mm FR4) = 0.035mm – not possible

4 layer PCB Pool – Internal to Internal (0.71mm FR4) = 0.27mm (100.2273ohms)

4 layer PCB Pool(possibly changed now??) – Internal to External (0.38mm FR4) = 0.12mm (100.9915ohms), or if too small then 0.15mm = (95.0631ohms)

4 layer PCB Train – Internal to Internal (0.99mm FR4) = 0.4mm (99.8636ohms)

4 layer PCB Train – Internal to External (0.22mm FR4, layer 2-3) = 0.05mm – not possible

4 layer PCB Train – Internal to External (1.245mm FR4, layer 1-3) = 0.49mm – not possible

75ohm Single Track Impedance

Also relevant to 75ohm radio antenna connections.Example track widths with GND plane under track

2 layer 1.6mm PCB (1.48mm FR4) = 1.29mm (75.0457ohms)

4 layer PCB Pool – Internal to Internal (0.71mm FR4) = 0.6mm (74.7938ohms)

4 layer PCB Pool(possibly changed now??) – Internal to External (0.38mm FR4) = 0.3mm (74.8156ohms)

50ohm Single Track Impedance

Also relevant to 50ohm radio antenna connections. Example track widths with GND plane under track

2 layer 1.6mm PCB (1.48mm FR4) = 2.65mm (50.1165ohms)

4 layer Multi-cb – Internal to External (0.14mm FR4) = 0.24mm (50.0744ohms)

4 layer PCB Train- Internal to External (0.22mm FR4) = 0.36mm (49.8393ohms)

4 layer PCB Pool – Internal to Internal (0.71mm FR4) = 1.25mm (50.0581ohms)

4 layer PCB Pool – Internal to External (0.38mm FR4) = 0.65mm (49.9609ohms)

Differential Pairs

Download the free Saturn PCB Design Toolkit – its a great tool for this. Use it as follows:

Select Differential Pairs

Select Imperial or Metric (you can select later and it will auto convert all values)

Set copper weights and plating thickness (e.g. 18um copper + 18um plating = 35micros (1oz))

Select internal or external layers (typically microstrip or embedded microstrip)

Enter substrate options (prepreg dielectric constant – typical PCB’s are FR4)

Enter track width in conductor width

Enter clearance between tracks in conductor distance

Enter prepreg height in conductor height (the distance between the copper layers excluding their thickness)

Click ‘solve’

Now adjust the track width and spacing until you get the impedance (Zdifferentail) you need. This is the thickness to make your tracks

USB 90ohm Differential Pair Track Impedance

USB 2.0 requires 90ohms differential impedance (max 45ohms per track)

Max trace-length mismatch between High-speed USB signal pairs should be no greater than 3.81mm.

Example track widths with GND plane under track

4 layer PCB Pool 1.6mm – Internal to External (0.38mm height – FR4 thickness to GND plane)

35um copper, track spacing 0.15mm and 0.38mm track width = 90.525ohms Zdifferential

35um copper, track spacing 0.2mm and 0.43mm track width = 90.174ohms Zdifferential

To stick with the max 45ohms per track (not practical for many designs):

35um copper, track spacing 1.4mm and 0.75mm track width = 89.118ohms Zdifferential

4 layer PCB Pool 1.6mm – Internal to Internal (0.71mm height – FR4 thickness to GND plane)

35um copper, track spacing 0.15mm and 0.61mm track width = 90.385ohms Zdifferential

4 layer PCB Train 1.6mm – Internal to Internal (0.99mm height – FR4 thickness to GND plane)

35um copper, track spacing 0.15mm and 0.8mm track width = 90.094ohms Zdifferential

4 layer PCB Train 1.6mm – Internal to External (0.22mm height – FR4 thickness to GND plane)

35um copper, track spacing 0.15mm and 0.26mm track width = 89.756ohms Zdifferential

35um copper, track spacing 0.2mm and 0.29mm track width = 90.28ohms Zdifferential

4 layer PCB Train 0.8mm – Internal to Internal (0.2mm height – FR4 thickness to GND plane)

35um copper, track spacing 0.2mm and 0.27mm track width = 90.217ohms Zdifferential

2 layer 1.6mm PCB (1.48mm FR4 thickness to GND plane)

35um copper, track spacing 0.15mm and 1.12mm track width = 90.184ohms Zdifferential

10/100Mbps Ethernet 100ohm Differential Pair Track Impedance

Ethernet requires 100ohms differential impedance (max 50ohms per track)

Example track widths with GND plane under track

4 layer PCB Pool – Internal to External (0.38mm height – FR4 thickness to GND plane)

35um copper, track spacing 0.15mm and 0.3mm track width = 100.462ohms Zdifferential

35um copper, track spacing 0.2mm and 0.34mm track width = 100.923ohms Zdifferential

To stick with the max 50ohms per track (not practical for many designs):

35um copper, track spacing 2.5mm and 0.65mm track width = 99.835ohms Zdifferential

If you use 1 of the plane layers with GND above and below (0.71mm & 0.38mm from track to GND planes) you get:

35um copper, track spacing 1.5mm and 0.42mm track width = 99.0.16ohms Zdifferential

um vs mm

There are 1000 micrometers in a millimeter.

0.1mm = 100um

1um = 0.001mm

Designing Your Own Layer Stackup

A PCB manufacturer starts with a core which is three pre-pressed layers consisting of: copper foil – prepreg – copper foil. The copper foil is typically available with a thickness of 18um, 35um, 70um, 105um or 140um. The core usually is specifies as an overall thickness with the prepreg thickness being the difference between the core specified thickness and the two copper foil layers (but it can sometimes be excluding the copper layers – check!).

For boards with 4 or more layers prepreg and foil layers are then also used around the core or multiple cores. A prepreg (pre-impregnated) is fibreglass impregnated with resin. The resin is pre-dried but not hardened so that when it is heated it flows and sticks, so the prepreg acts a the glue between the addiional layers be it stick 2 cores together of sticking a core to an outside layer of copper foil.. The name of each prepregs derives from the type of fibreglass used.

Finally the outer copper foil layers are plated

There are some rules how to build your stackup. Not every combination is possible. Check with your PCB manufacturer.

Good reources

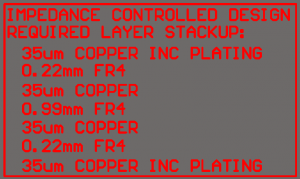

Ensure Your PCB IS Made With The Right Stackup

Its a good idea to include the required stackup on one of your copper layers to ensure it is used. Something like this:

9 years ago

why 90 ohm required for usb? why not 100 ohm

9 years ago

why reference plane required?

8 years ago

could you please share the analytical or mathematical proof to decide the matching impedance for SPI, UART, I2C, USB and LVDS lines?????