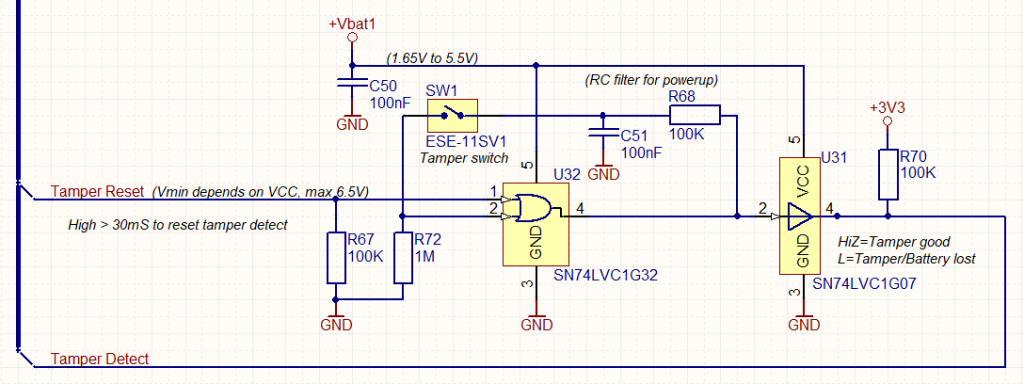

Simple battery backed up, switch released detect circuit

Circuit is 3.3V powered and has a battery. We want to detect if the tamper switch is ever released, even when the 3.3V power is off, so that when next powered up the fact that the tamper switch got released at any time can be determined.

USEFUL?

We benefit hugely from resources on the web so we decided we should try and give back some of our knowledge and resources to the community by opening up many of our company’s internal notes and libraries through resources like this. We hope you find it helpful.

Please feel free to comment if you can add help to this page or point out issues and solutions you have found, but please note that we do not provide support here. If you need help with a problem please use one of the many online forums.

5 years ago

Q: doesn’t this tamper detect circuit require some state memory? I don’t see a flip-flop.

A: the U32 OR gate is in a feedback topology through SW1 that creates a latch to store the circuit state.

Q: why is U31 needed? what is it’s purpose?

A: U31 is an open-drain buffer that isolates the U32 latched state from the U31 Tamper Detect output, necessary because there are two power domains in the circuit +VBat1 and +3V3 which operate independently. Without U31 there would a problem when +3V3 (e.g., the microprocessor power supply for the not shown CMOS receiver monitoring Tamper Detect) is turned off but +Vbat1 (e.g. a coin cell battery backup) is still on. The high output of U32 would be driving into the unpowered CMOS input, causing back-powering of the +3V3 domain through the CMOS input’s protection diodes and a significant power draw on +Vbat1 that will quickly deplete the battery, not to mention potential power-up violations for the rest of the +3V3 circuits. U31 isolates the +Vbat domain, using R70 instead of +Vbat to signal high so that Tamper Detect signal never exceeds the +3V3 power rail voltage.

Q: what is the initial state of this circuit at power up of Vbat1? Does it reliably detect when +Vbat1 power was lost and indicate possible tamper with U31 output low?

A: The C51 cap is important here and will determine the startup state via U32 pin 2, assuming Tamper Reset is low and SW1 is closed (no tamper – normal). As +Vbat1 voltage ramps up the logic behavior of the U32 OR gate may not be guaranteed while VCC (pin5) is below the VCC_min of the part. Depending on the U32 internal circuitry, the U32 pin 4 output could glitch high during +Vbat1 power up. Without C51 cap, such a glitch could cause the circuit to startup latched in the high state instead. With C51 at 0V temporarily holding U32 pin 2 low, assuming C51 was discharged before power up through R72, the circuit properly initializes in the latched low state.

5 years ago

Nice explanation, thanks :-)